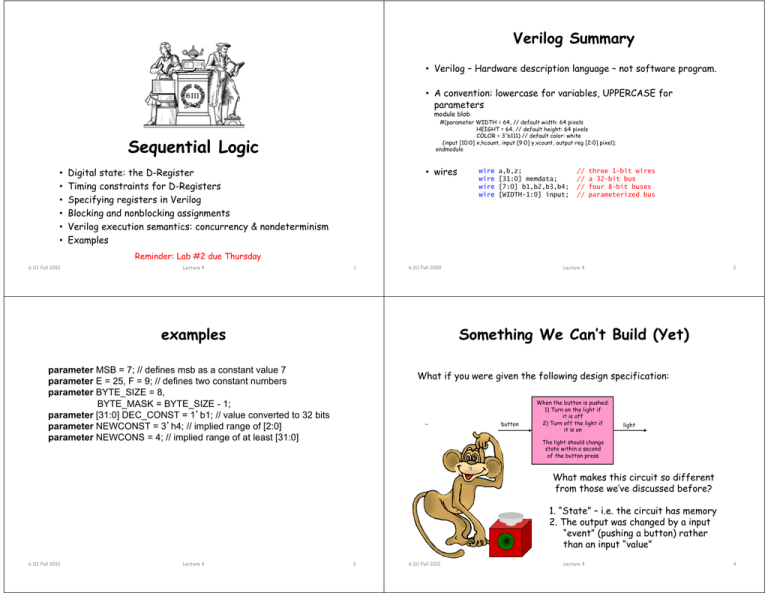

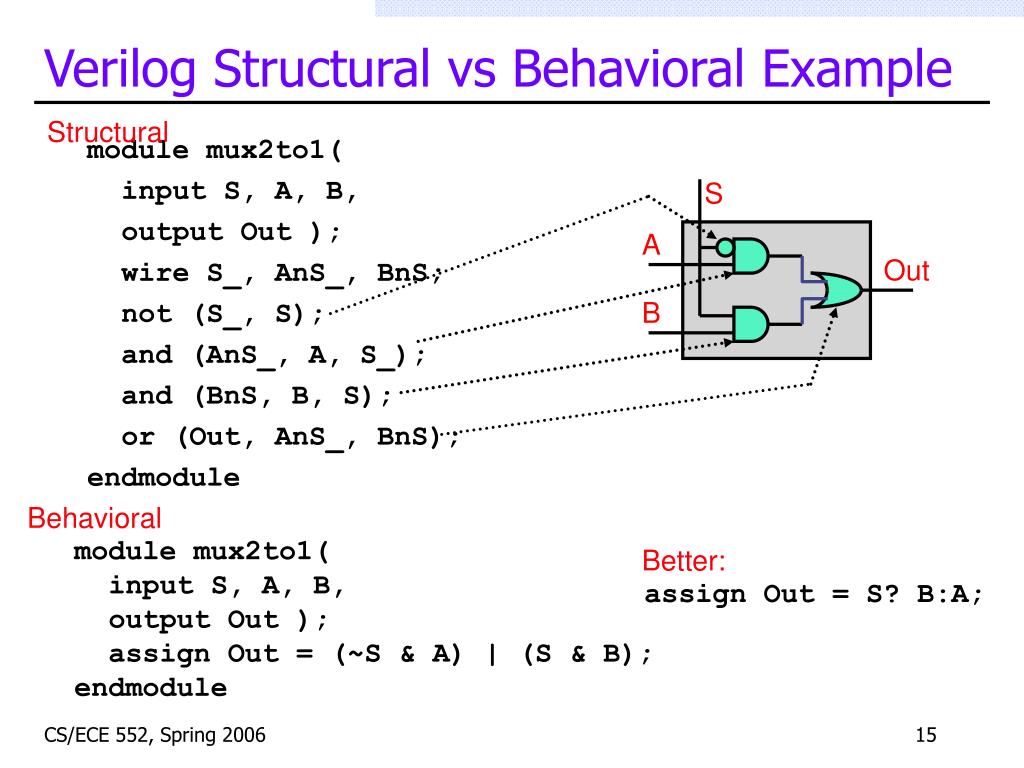

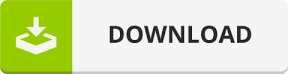

Specify which features are synthesizable that depends on the tooling used. It is interesting to note however that the specification of Verilog does not Register-transfer- and gate-level design. Typical modern hardware design uses a mix of RTL design specifies a circuit in terms of dataįlow through registers and logical operations. Procedural features of Verilog (with little regard for the structural

Generally with fewer features at lower levels. Hardware synthesis, each level of abstraction uses a different language subset, The language provides specific features to serve each of these purposes. specification of formal properties and.structural/register-transfer level ( RTL).circuit design/specification at different levels of abstraction:.Language, serving distinct purposes of modern hardware design. (which subsumed SystemVerilog as of the 2009 standardisation) is a unified The languageĪ subset of Verilog is used for specifying synthesizable circuits. Using those features, and the tooling support for a design. Particular features of the language to use, the style and idioms employed in AĬompounding issue is that complex hardware designs rely on a complexĪs I see it, there are three aspects to writing synthesizable Verilog code: the Only through disciplined/idiomatic use, can efficient designs be implemented.

This is because Verilog provides little abstraction of hardware structures, and Mindset associated with using a language to describe hardware circuits. Python, it has been interesting to experience the contrasting philosophy and

Coming from a software background where I was mainly using C/C++ and In the last year, I’ve started from scratch writing Verilog for hardwareĭesign.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed